# Virtual Fabrication of Short-Channel Recessed-Source/Drain (Re-S/D) SOI MOSFETs

Srikanya Dasari, Gopi Krishna Saramekala and Pramod Kumar Tiwari Department of Electronics and Communication Engineering National Institute of Technology, Rourkela-769008, India tiwarip@nitrkl.ac.in

**Abstract**—This paper describes process and device simulation results of short-channel Recessed-Source/Drain (Re-S/D) SOI MOSFETs. A Re-S/D SOI MOSFET with 30nm channel length, and 10nm channel thickness, is virtually fabricated with reduced short channel effects (SCEs) and low source/drain series resistance. The processing steps, which are required to obtain the structure of the Re-S/D SOI MOSFET, are proposed and explained in detail. The electrical characteristic  $I_{ds}$  versus drain to source voltage  $V_{DS}$  is obtained for different values of  $V_{GS}$  and Re-S/D thickness ( $t_{rsd}$ ). The device is virtually fabricated using 2D process simulator ATHENA, followed by electrical characterization which is done with the help of device simulator ATLAS<sup>TM</sup> from SILVACO.

#### Keywords— Short Channel Effects (SCEs); Recessed-Source/Drain (*Re-S/D*) thickness; electrical characteristics.

#### I. INTRODUCTION

Scaling down of MOSFET device in IC Technology offers excellent features such as packaging density and device speed of operation which increase exponentially. Simultaneously, power dissipation decreases exponentially as stated by Moore's law [1-2]. However, leakage current and short channel effects (SCEs) are to be considered when MOSFETs are scaled to the deep submicron region [3]. In order to facilitate MOSFET scaling and to follow the Moore's law, fully depleted(FD) ultra thin body (UTB) SOI MOSFET could be preferred[4]. SOI devices increase the device speed by 20 -30% and reduces power dissipation to 50% of conventional MOSFETs [5]. Further, the FD SOI MOSFETs offer reduced short-channel effects (SCEs), smaller subthreshold swing, less mobility degradation and high on-to-off current ratio when compared with conventional MOSFET devices. Sapna et al. [6]. have virtually fabricated 35nm channel length fully depleted (FD) SOI MOSFET with 6nm thick SOI layer using ATHENA process simulator. The results of the study led to the conclusions that threshold voltage and subthreshold swing decrease with the decrease in SOI layer thickness. However, the on-current driving-capability of the device is limited by a demerit of large series resistance, which is associated with ultra thin body (UTB) of (FD) SOI MOSFETs [7].

Zhang *et al.* [8] fabricated self-aligned recessedsource/drain (Re-S/D) fully depleted (FD) UTB SOI MOSFET. They stated that the series resistance and the miller capacitance got reduced over UTB SOI MOSFETs when the source and drain regions are extended deeper into the buried oxide. Apart from this, slight DIBL effect is also observed. Later on Chang *et al.* [9] successfully fabricated 30nm channel length Re-S/D SOI MOSFET with 5nm thick undoped channel. They demonstrated the reduction in source/drain series resistance by extending heavily doped polysilicon source/drain regions into the buried oxide (BOX) of SOI wafer. It was found that the proposed device exhibited excellent properties in short channel immunities such as draininduced barrier lowering (DIBL) and sub threshold slope. Svilicic *et al.*[10] have reported theoretical models for the potential distributions, short-channel threshold voltage and subthreshold swing of the Re-S/D UTB SOI MOSFETs.

In our previous work [11-13], we have analyzed the subthreshold characteristics of Re-S/D SOI MOSFETs analytically by presenting analytical subthreshold current and subthreshold swing models. We have observed that the oncurrent driving-capability of a Re-S/D UTB SOI MOSFETs could be further improved by adopting the dual- metal-gate (DMG) structure instead of conventional single-metal-gate structure. The present paper describes the virtual fabrication of 30nm channel length Re-S/D SOI MOSFET using ATHENA. The main objective of ATHENA process simulator [14] is to create a device structure that is used by the ATLAS device simulator [14] for further electrical characterization of the device. ATHENA provides an appropriate and suitable platform for simulating processes such as oxidation, lithography, physical etching and deposition, diffusion, ion implantation which are used in semiconductor industry. Twodimensional (2D) process simulator ATHENA offers good features such as - fast and accurate simulation of the device; replacement of costly wafer experiments with simulations; providing advanced simulation environment

#### II. VIRTUAL FABRICATION OF THE DEVICE

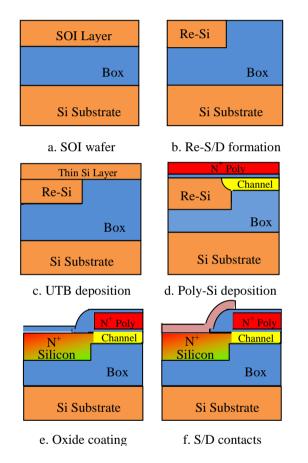

Schematics of Fig.1 show the proposed process flow of Re-S/D SOI MOSFET. We consider a symmetrical MOSFET i.e. the regions from the center of the channel to source and center of the channel to the drain are identical to each other. Hence, we use a special facility from ATHENA that half of the structure (region from center of the channel to source) is fabricated first and then the other half structure (region from center of the channel to drain) is generated using the command "structure mirror". The process flow of Re-S/D SOI MOSFET commenced with defining the initial simulation grid. Specifically, the simulation grid represents the points where the model equations are solved. The number of nodes in a grid

#### Proceedings of International Symposium on Semiconductor Materials and Devices (ISSMD-3), 2-5' February 2015 Catagory: Semiconductor Nanostructures

has a direct influence on simulation time and accuracy of the device. Therefore, specification of simulation grid plays a crucial role. So, a finer grid should exist only in the critical areas of the device where ion implantation will occur, where junctions will be formed.

P-type <100> SOI wafer with 400nm thick Si substrate, 180nm thick buried oxide (BOX), 20nm thick SOI layer and background doping of  $10^{14}$  cm<sup>-3</sup> are considered as shown in Fig 1(a). The process of creating Re- S/D above the BOX is as follows: Firstly, SOI layer is etched by using geometrical etching technique and then oxide layer with thickness greater than silicon layer thickness is deposited using conformal deposition technique. After that, etching of oxide is carried out to planar structure as shown in Fig 1(b). Again, conformal deposition technique is used to deposit Si layer of thickness 20nm which is exposed to perform further processing steps as

Fig. 1. Schematics showing a process flow for the proposed Re-S/D SOI  ${\it MOSFET}$

shown in Fig 1(c). Dry oxidation is performed at  $1000^{\circ}$ C for 30 minutes in dry O<sub>2</sub> at 1 atmospheric pressure with the addition of 3% HCl. Following oxide (SiO<sub>2</sub>) growth, the oxide is etched back to a precise thickness to facilitate ion implantation that comes in the next step. Subsequently, the top Si layer is thinned to 10nm by thermal oxidation process. Further, Boron ion implantation is carried out at 7KeV of implantation energy with dosage of  $3 \times 10^{12}$  cm<sup>-3</sup> in the channel region.

Furthermore, gate oxide (SiO<sub>2</sub>) layer is developed by dry oxidation process which is performed at relatively low temperature of 850° C for a small time interval of 3 minutes. Heavily doped poly-silicon which is advantageous in terms of its high conductivity is utilized as gate instead of metal. Poly silicon of thickness 40nm is doped with phosphorus of concentration 10<sup>18</sup> cm<sup>-3</sup> and deposited with conformal deposition technique as shown in Fig 1(d). The next process is development of source/drain (S/D) using the two implantations: phosphorous and arsenic. These implantations are followed by some drive-in diffusions, which are performed at 800<sup>°</sup>C in nitrogen for 11 minutes. If the voltage levels are not scaled simultaneously with the shrinking size of the device, there may be a rise in the electric field in the channel region resulting in hot electron current, in which electrons approach quickly, scattering into the gate oxide region.

To overcome this problem phosphorous implantation is carried out to create a lightly doped drain (LDD) region, which decreases electron energy gradually as electrons

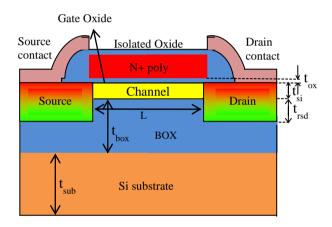

Fig. 2. Schematic showing a structure of Re-S/D SOI MOSFET

approach the drain. Arsenic implantation is carried out with high dosage of  $5 \times 10^{14}$  cm<sup>-3</sup> and the implant energy is 15keV to build the low resistance in the source and drain region as shown in Fig 1(e). For providing electrical contact to the source/drain, Aluminum (Al) is deposited. Later, oxide on the left side of the device is etched for depositing Al of thickness 20nm and the contact is shaped by etching part of the aluminum on the right side as shown in Fig 1(f). This completes the virtual fabrication of half of the device. On mirror imaging the above obtained half structure the full structure of Re-S/D SOI MOSFET is formed. This completes the simulation of other half. Fig. 2 shows the schematic of complete structure of Recessed-S/D SOI MOSFET. The symbols L,  $t_{Si}$  ,  $t_{ox,}$   $t_{box}$  and  $t_{rsd}$  represent the gate length, channel thickness, gate oxide thickness buried oxide (BOX) depth and recessed source/drain (Re-S/D) thickness respectively.

# III. RESULTS AND DISCUSSION

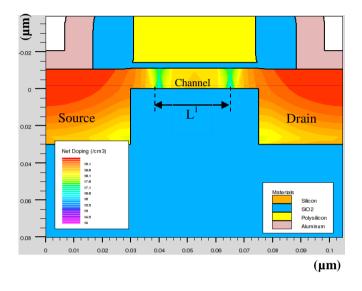

This section is aimed to discuss the doping and electrical characterization of device using ATLAS device simulator. The structure utilized for the simulation is generated by ATHENA process simulator. Fig. 3 shows the variation of net doping in source, channel and drain regions of 45nm channel length Re-S/D SOI MOSFET. The heavily doped n-type source/drain regions are formed by arsenic implantation with an energy of 20 keV and a dosage of  $5 \times 10^{13}$  cm<sup>-3</sup>. The channel region is doped with boron impurity, with an implant energy of 7 keV and a dosage of  $5 \times 10^{13}$  cm<sup>-3</sup>. The ion beam used for both implantations is tilted by  $7^0$  and rotated by  $30^0$ . The peak concentration in the source /drain regions and channel regions are observed as  $5 \times 10^{19}$  cm<sup>-3</sup>,  $3 \times 10^{18}$  cm<sup>-3</sup> respectively.

Fig. 3. Schematic diagram of net doping in source, channel and drain regions of a Re-S/D SOI MOSFET

where, tsi=10nm L=45nm L1=30nm tox=3.2nm tbox=200nm trsd=20nm

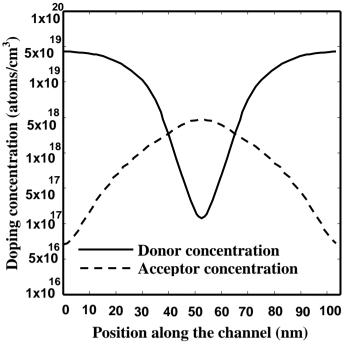

Fig. 4 shows the acceptor and donor doping profile along the cutline taken from source to drain region. The effective channel length (L1) of the device becomes 30nm due to lateral penetration of source/drain implantation

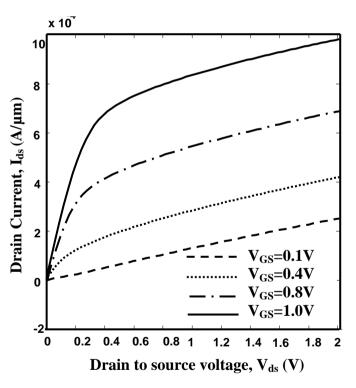

Fig. 5 shows drain current ( $I_{ds}$ ) plot with respect to drain to source voltage ( $V_{DS}$ ) for different gate to source voltages ( $V_{GS}$ ) considering a step of 0.4V. The drain current ( $I_{ds}$ ) is found to be increased with drain to source voltage ( $V_{DS}$ ).

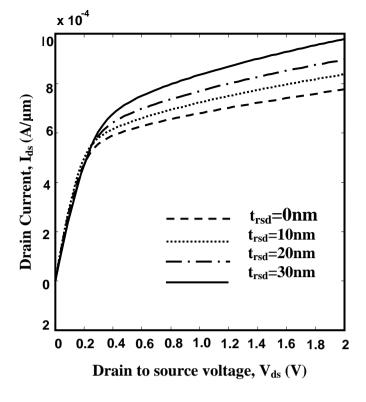

Fig. 6 shows the effect of recessed source/drain thickness  $(t_{rsd})$  on drain current  $(I_{ds})$  by keeping all other device parameters constant. It also depicts the  $I_{ds}$ -V<sub>DS</sub> characteristics of Re-S/D SOI MOSFET where  $t_{rsd}$  varies from 0 to 30nm with step size of 10nm; when  $t_{rsd}$ =0nm, the device simply replicates conventional SOI MOSFET. From this figure it is observed that the on-current driving capability of the device increases with recessed-S/D thickness ( $t_{rsd}$ ).

*Fig. 4 Acceptor and donor doping profile along the cutline* where, tsi=10nm L=45nm L1=30nm tox=3.2nm tbox=200nm trsd=20nm

Fig. 5. Drain current versus Drain to source voltage for different Gate to source values.

where, tsi=10nm L=30nm tox=3.2nm tbox=200nm trsd=20nm

Fig. 6 Drain current versus Drain to source voltage for Recessed source/drain thickness values.

where,  $t_{si}$ =10nm L=30nm  $t_{ox}$ =3.2nm  $t_{box}$ =200nm  $t_{rsd}$ =20nm  $V_{GS}$ =1V

# IV. CONCLUSIONS

In this paper, the virtual fabrication of a recessed-S/D SOI with channel length of 30nm has been done. MOSFET Several processing steps such as oxidation, deposition, etching, ion implantation and lithography have been utilized in the process of device fabrication. Gate oxide thickness  $(t_{ox})$ which is 3.2nm is extracted by process parameter extraction. The thickness of the Re-S/D (t<sub>rsd</sub>) is controlled by SOI layer thickness. The electrical characteristics such as drain current (Ids) versus drain to source voltage (VDS) have been explored for different values of gate to source voltage (V<sub>GS</sub>). Also variation of drain current  $(I_{ds})$  with the drain to source  $(V_{DS})$ voltage for different values of recessed S/D thickness (t<sub>rsd</sub>) have been evaluated. The drain current (Ids) of the device increased with increasing source/drain penetration in buried oxide(BOX).

# ACKNOWLEDGMENT

The present work is financially supported by Science and Engineering Research Board (SERB), Department of Science and Technology (DST), Govt. of India, under the fast track scheme for young scientists. The project number is SERC/ET-0415/2012.

# REFERENCES

- [1] "The International Technology Roadmap for Semiconductors", 2013 Edition.

- [2] Gordon E. Moore "Cramming more components onto integrated circuits, computer history museum" Electronics, 1965.

- [3] H. Iwai, "Roadmap for 22 nm and beyond", Microelectronic Engineering, vol.86, pp. 1520-1528, 2009.

- [4] Vishwas Jaju, Vikram Dalal, "Silicon-on-Insulator Technology", Advances in MOSFETs, pp.1-12, Spring 2004.

- [5] M. Jagadesh Kumar, Anurag Chaudhry, "Two-Dimensional Analytical Modeling of Fully Depleted DMG SOI MOSFET and Evidence for Diminished SCEs", IEEE Transactions on Electron Devices, vol. 51, pp.569-574, 2004.

- [6] Sapna, Bijender Mehandia, "Study of Electrical Characteristics of SOI MOSFET Using Silvaco TCAD Simulator", Current Trends in Technology and Sciences VOL. 1, pp 15-18, July-2012.

- [7] Alberto O. Adan and Kenichi Higashi," OFF-State Leakage Current Mechanisms in BulkSi and SOI MOSFETs and Their Impact on CMOS ULSIs Standby Current", IEEE IEEE Transactions on Electron Devices, vol. 48, no. 9, pp.2050-2057, september 2001.

- [8] Zhikuan Zhang, Shengdong Zhang, and Mansun Chan, "Self-Align Recessed Source Drain Ultrathin Body SOI MOSFET", IEEE Electron Device Letters, vol. 25, no. 11, pp.740-742, november 2004.

- [9] Chang-Geun Ahn, Won-Ju Cho, Kiju Im, Jong-Heon Yang, In-Bok Baek, Sungkweon Baek and Seongjae Lee, " 30-nm Recessed S/D SOI MOSFETWith an Ultrathin Body and a Low SDE Resistance", IEEE electron device letters, vol. 26, no. 7, pp.486-488, july 2005.

- [10] B. Svilicic, V. Jovanovic and T. Suligoj " Analytical models of frontand back-gate potential distribution and threshold voltage for recessed source/drain UTB SOI MOSFETs", Solid-State Electronics VOL. 53, pp. 540-547, 2009

- [11] Gopi krishna Saramekala, Sarvesh Dubey, Pramod kumar Tiwari, " Numerical simulation based study of analog and RF performance of a Re-S/D SOI MOSFETs" Supperlattices and Microstructures Journal, Volume 76, , pp.77–89, December 2014

- [12] Gopi Krishna S., Abirmoya Santra, Pramod Kumar Tiwari, Analytical subthreshold current and subthreshold swing models for a short-channel dual-metal-gate (DMG) fully depleted recessed-source/drain (Re-S/D) SOI MOSFET, Journal of Computaional Electronics, vol 13, pp.467-476, 2014

- [13] Ajit Kumar, Pramod Kumar Tiwari, A threshold voltage modeling of Re-S/D SOI MOSFETs including SISP effects, Solid State Electronics, vol 95, issue 5, pp.52-60, 2014

- [14] ATLAS Users Manual, Silvaco International, Santa Clara, CA (2012).